# **ASSP**

# Power Supply Monitor with Watch-Dog Timer

# **MB3773**

#### **■** DESCRIPTION

MB3773 generates the reset signal to protect an arbitrary system when the power-supply voltage momentarily is intercepted or decreased. It is IC for the power-supply voltage watch and "Power on reset" is generated at the normal return of the power supply. MB3773 sends the microprocessor the reset signal when decreasing more than the voltage, which the power supply of the system specified, and the computer data is protected from an accidental deletion.

In addition, the watchdog timer for the operation diagnosis of the system is built into, and various microprocessor systems can provide the fail-safe function. If MB3773 does not receive the clock pulse from the processor for an specified period, MB3773 generates the reset signal.

#### **■ FEATURES**

- Precision voltage detection (Vs =  $4.2 \text{ V} \pm 2.5 \text{ \%}$ )

- Detection threshold voltage has hysteresis function

- Low voltage output for reset signal (Vcc = 0.8 V Typ)

- Precision reference voltage output ( $V_R = 1.245 \text{ V} \pm 1.5\%$ )

- With built-in watchdog timer of edge trigger input.

- External parts are few.(1 piece in capacity)

- The reset signal outputs the positive and negative both theories reason.

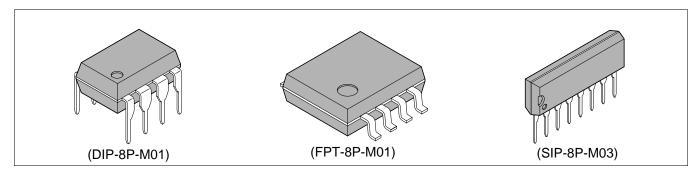

#### ■ PACKAGES

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

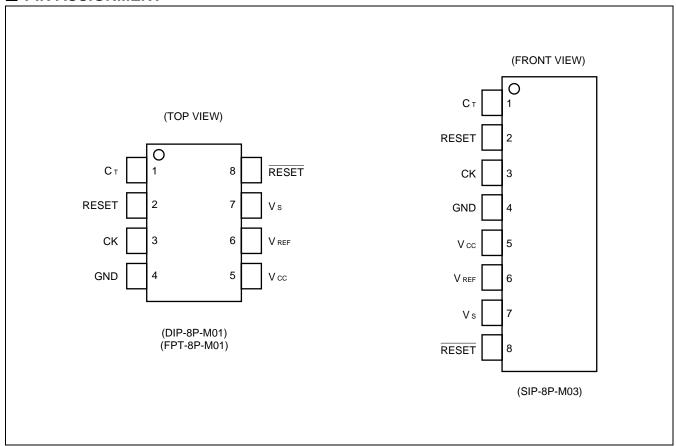

## **■ PIN ASSIGNMENT**

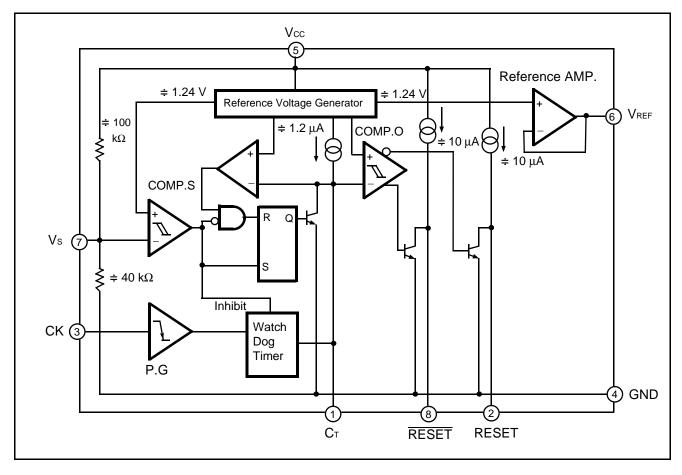

## **■ BLOCK DIAGRAM**

#### **■ FUNCTIONAL DESCRIPTIONS**

Comp.S is comparator including hysteresis. it compare the reference voltage and the voltage of Vs, so that when the voltage of Vs terminal falls below approximately 1.23 V, reset signal outputs.

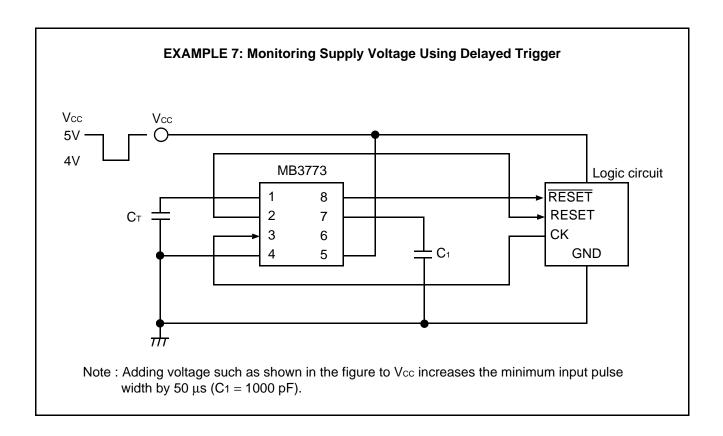

Instantaneous breaks or drops in the power can be detected as abnormal conditions by the MB3773 within a 2 µs interval.

However because momentary breaks or drops of this duration do not cause problems in actual systems in some cases, a delayed trigger function can be created by connecting capacitors to the Vs terminal.

Comp.O is comparator for turning on/off the output and, compare the voltage of the Cr terminal and the threshold voltage. Because the RESET/RESET outputs have built-in pull-up circuit, there is no need to connect to external pull-up resistor when connected to a high impedance load such as CMOS logic IC.

(It corresponds to 500 k $\Omega$  at Vcc = 5 V.) when the voltage of the CK terminal changes from the "high" level into the "Low" level, pulse generator is sent to the watch-dog timer by generating the pulse momentarily at the time of drop from the threshold level.

When power-supply voltages fall more than detecting voltages, the watch-dog timer becomes a interdiction. The Reference amplifier is a op-amp to output the reference voltage.

If the comparator is put up outside, two or more power-supply voltage monitor and overvoltage monitor can be done.

If it uses a comparator of the open-collector output, and the output of the comparator is connected with the Vs terminal of MB3773 without the pull-up resistor, it is possible to voltage monitor with reset-hold time.

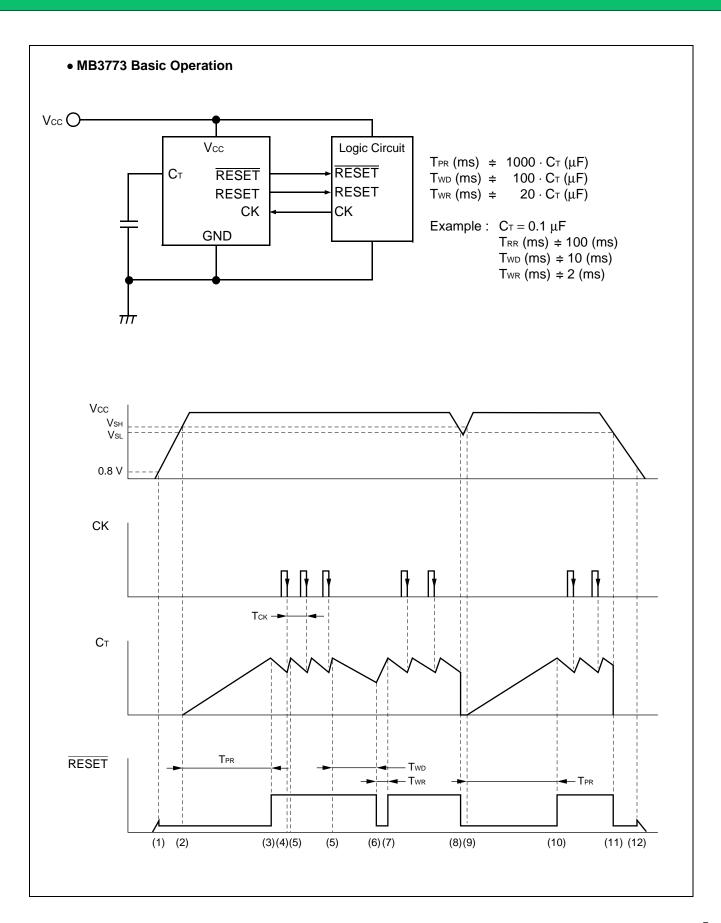

#### **■ OPERATION SEQUENCE**

- (1) When Vcc rises to about 0.8 V,  $\overline{\text{RESET}}$  goes "Low" and RESET goes "High". The pull-up current of approximately 1  $\mu$ A (Vcc = 0.8 V) is output from RESET.

- (2) When Vcc rises to V<sub>SH</sub> ( $\pm$  4.3V), the charge with C<sub>T</sub> starts. At this time, the output is being reset.

- (3) When C<sub>T</sub> begins charging, RESET goes "High" and RESET goes "Low".

After TPR reset of the output is released.

Reset hold time:  $T_{PR}$  (ms)  $\Rightarrow$  1000  $\times$   $C_{T}$  ( $\mu$ F)

After releasing reset, the discharge of C<sub>T</sub> starts, and watch-dog timer operation starts.

TPR is not influenced by the CK input.

- (4) C changes from the discharge into the charge if the clock (Negative edge) is input to the CK terminal while discharging C<sub>T</sub>.

- (5) C changes from the charge into the discharge when the voltage of  $C_T$  reaches a constant threshold ( $\pm$  1.4 V).

- (4) and (5) are repeated while a normal clock is input by the logic system.

Discharge time of C<sub>T</sub> until reset is output: Two is watch-dog timer monitoring time.

Two (ms)  $\Rightarrow$  100  $\times$  CT ( $\mu$ F)

Because the charging time of  $C_T$  is added at accurate time from stop of the clock and getting to the output of reset of the clock,  $T_{WD}$  becomes maximum  $T_{WD} + T_{WR}$  by minimum  $T_{WD}$ .

(7) Reset time in operating watch-dog timer:TwR is charging time where the voltage of C<sub>T</sub> goes up to off threshold (≠ 1.4 V) for reset.

Twr (ms)  $\neq$  20  $\times$  CT ( $\mu$ F)

Reset of the output is released after  $C_T$  reaches an off threshold for reset, and  $C_T$  starts the discharge, after that if the clock is normally input, operation repeats (4) and (5), when the clock is cut off, operation repeats (6) and (7).

- (8) When Vcc falls on  $V_{SL}$  ( $\Rightarrow$  4.2 V), reset is output.  $C_T$  is rapidly discharged of at the same time.

- (9) When Vcc goes up to VsH, the charge with CT is started.

When Vcc is momentarily low,

After falling V<sub>SL</sub> or less Vcc, the time to going up is the standard value of the Vcc input pulse width in V<sub>SH</sub> or more

After the charge of C<sub>T</sub> is discharged, the charge is started if it is T<sub>Pl</sub> or more.

- (10) Reset of the output is released after TPR, after Vcc becomes VsH or more, and the watch-dog timer starts. After that, when Vcc becomes VsL or less, (8) to (10) is repeated.

- (11) While power supply is off, when Vcc becomes VsL or less, reset is output.

- (12) The reset output is maintained until Vcc becomes 0.8 V when Vcc falls on 0 V.

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                       | Cumbal         | Rat         | Unit               |       |

|---------------------------------|----------------|-------------|--------------------|-------|

| raiailletei                     | Symbol         | Min         | Max                | Offic |

| Supply voltage                  | Vcc            | - 0.3       | + 18               | V     |

| Input voltage                   | Vs             | - 0.3       | Vcc + 0.3 ( ≤ +18) | V     |

| Input voltage                   | Vск            | - 0.3       | + 18               | V     |

| RESET, RESET Supply voltage     | Vон            | - 0.3       | Vcc + 0.3 ( ≤ +18) | V     |

| Power dissipation (Ta ≤ +85 °C) | P <sub>D</sub> | _           | 200                | mW    |

| Storage temperature             | Тѕтс           | <b>– 55</b> | + 125              | °C    |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                     | Symbol      | Value       |      | Unit |

|-------------------------------|-------------|-------------|------|------|

| rarameter                     |             | Min         | Max  | Onit |

| Supply voltage                | Vcc         | + 3.5       | + 16 | V    |

| RESET, RESET sink current     | loL         | 0           | 20   | mA   |

| VREF output current           | Іоит        | - 200       | + 5  | μΑ   |

| Watch clock setting time      | <b>t</b> wD | 0.1         | 1000 | ms   |

| CK Rising/falling time        | trc, trc    | _           | 100  | μs   |

| Terminal capacitance          | Ст          | 0.001       | 10   | μF   |

| Operating ambient temperature | Та          | <b>- 40</b> | + 85 | °C   |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

## **■ ELECTORICAL CHARACTERISTICS**

## (1) DC Characteristics

(Vcc = 5 V, Ta = + 25 °C)

|                                              |                   |                                                                                       | (Vcc = 5 V, Ta = + |       |       | 20 0  |

|----------------------------------------------|-------------------|---------------------------------------------------------------------------------------|--------------------|-------|-------|-------|

| Parameter                                    | Symbol            | Condition                                                                             | ļ                  |       |       | Unit  |

|                                              |                   |                                                                                       | Min                | Тур   | Max   | Oilit |

| Supply current                               | lcc               | Watch dog timer operating                                                             |                    | 600   | 900   | μΑ    |

|                                              | VsL               | Vcc                                                                                   | 4.10               | 4.20  | 4.30  |       |

| Detection voltage                            | VOL               | Ta = $-40$ °C to $+85$ °C                                                             | 4.05               | 4.20  | 4.35  | V     |

| Detection voltage                            | Vsh               | Vcc                                                                                   | 4.20               | 4.30  | 4.40  | v     |

|                                              | VSH               | Ta = $-40$ °C to $+85$ °C                                                             | 4.15               | 4.30  | 4.45  |       |

| Hysteresis width                             | V <sub>H</sub> ys | Vcc                                                                                   | 50                 | 100   | 150   | mV    |

| Reference voltage                            | V <sub>REF</sub>  | _                                                                                     | 1.227              | 1.245 | 1.263 | V     |

| Treference voltage                           | VKEF              | Ta = - 40 °C to + 85 °C                                                               | 1.215              | 1.245 | 1.275 |       |

| Reference voltage change rate                | $\Delta V_{REF1}$ | Vcc = 3.5 V to 16 V                                                                   | _                  | 3     | 10    | mV    |

| Reference voltage output loading change rate | $\Delta V_{REF2}$ | $I$ оит = $-200 \mu A$ to $+5 \mu A$                                                  | - 5                | _     | + 5   | mV    |

| CK threshold voltage                         | Vтн               | Ta = - 40 °C to + 85 °C                                                               | 0.8                | 1.25  | 2.0   | V     |

| CK input current                             | Іін               | Vck = 5.0 V                                                                           | _                  | 0     | 1.0   | μΑ    |

| CK input current                             | lıL               | Vck = 0.0 V                                                                           | - 1.0              | - 0.1 | _     |       |

| C⊤ discharge current                         | Істр              | Watch dog timer operating VcT = 1.0 V                                                 | 7                  | 10    | 14    | μΑ    |

| High level output voltage                    | V <sub>OH1</sub>  | Vs open, IRESET = -5 μA                                                               | 4.5                | 4.9   | _     | \/    |

|                                              | V <sub>OH2</sub>  | $Vs = 0 V$ , $I_{RESET} = -5 \mu A$                                                   | 4.5                | 4.9   | _     | V     |

|                                              | V <sub>OL1</sub>  | Vs = 0 V, IRESET = 3 mA                                                               | _                  | 0.2   | 0.4   | - V   |

| Output seturation valtage                    | V <sub>OL2</sub>  | Vs = 0 V, IRESET = 10 mA                                                              | _                  | 0.3   | 0.5   |       |

| Output saturation voltage                    | V <sub>OL3</sub>  | Vs open, Ireset = 3 mA                                                                | _                  | 0.2   | 0.4   |       |

|                                              | V <sub>OL4</sub>  | Vs open, Ireset = 10 mA                                                               | _                  | 0.3   | 0.5   |       |

| Output sink ourrant                          | lOL1              | Vs = 0 V, VRESET = 1.0 V                                                              | 20                 | 60    | _     | - mA  |

| Output sink current                          | lol2              | Vs open, Vreset = 1.0 V                                                               | 20                 | 60    | _     |       |

| C⊤ charge current                            | Істи              | Power on reset operating VcT = 1.0 V                                                  | 0.5                | 1.2   | 2.5   | μΑ    |

| Min supply voltage for RESET                 | Vccl1             | VRESET = 0.4 V,<br>IRESET = 0.2 mA                                                    | _                  | 0.8   | 1.2   | V     |

| Min supply voltage for RESET                 | Vccl2             | $V_{RESET} = V_{CC} - 0.1 \text{ V},$ $R_L \text{ (pin 2 - GND)} = 1 \text{ M}\Omega$ | _                  | 0.8   | 1.2   | V     |

## (2)AC Characteristics

(Vcc = 5 V, Ta = + 25 °C)

| Parameter                     | Symbol Condition | Value                                                                            |     |     | Unit |       |

|-------------------------------|------------------|----------------------------------------------------------------------------------|-----|-----|------|-------|

| raiametei                     | Зуппоот          | Symbol                                                                           |     | Тур | Max  | Oilit |

| Vcc input pulse width         | Ты               | 5 V Vcc 4 V                                                                      | 8.0 |     | _    | μs    |

| CK input pulse width          | Тскw             | CKor                                                                             | 3.0 |     | _    | μs    |

| CK input frequency            | Тск              | _                                                                                | 20  | _   | _    | μs    |

| Watch dog timer watching time | Twd              | $C_T = 0.1 \ \mu F$                                                              | 5   | 10  | 15   | ms    |

| Watch dog timer reset time    | Twr              | $C_T = 0.1 \mu F$                                                                | 1   | 2   | 3    | ms    |

| Rising reset hold time        | Tpr              | Cτ = 0.1 μF, Vcc                                                                 | 50  | 100 | 150  | ms    |

| Output propagation            | T <sub>PD1</sub> | $\overline{\text{RESET}}$ , $R_L = 2.2 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$ | _   | 2   | 10   | 116   |

| delay time from Vcc           | T <sub>PD2</sub> | RESET, $R_L = 2.2 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$                      | _   | 3   | 10   | μѕ    |

| Output rising time*           | <b>t</b> R       | $\begin{aligned} R_L &= 2.2 \ k\Omega, \\ C_L &= 100 \ pF \end{aligned}$         |     | 1.0 | 1.5  | 116   |

| Output falling time*          | t <sub>F</sub>   | $\begin{aligned} R_L &= 2.2 \ k\Omega, \\ C_L &= 100 \ pF \end{aligned}$         |     | 0.1 | 0.5  | μѕ    |

$<sup>^{\</sup>star}$  : Output rising/falling time are measured at 10 % to 90 % of voltage.

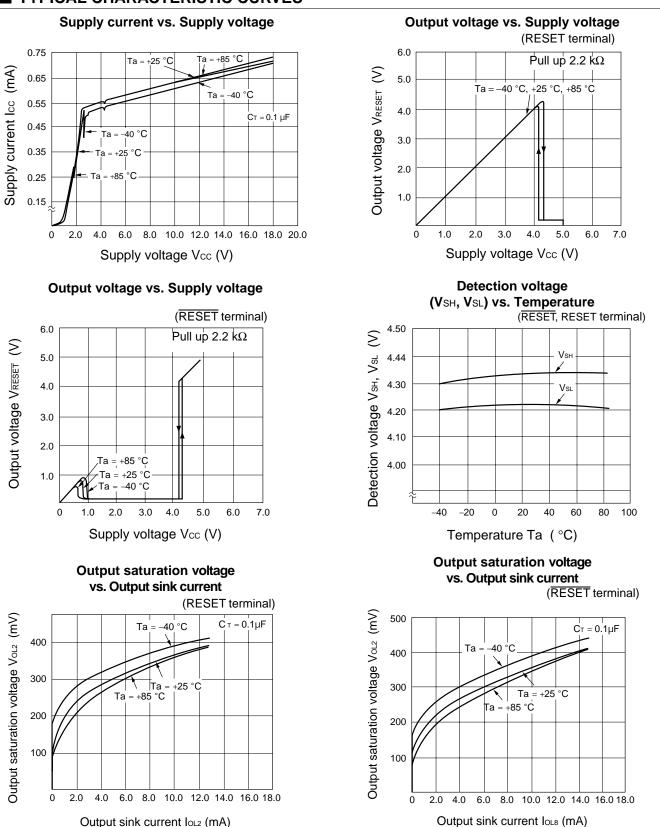

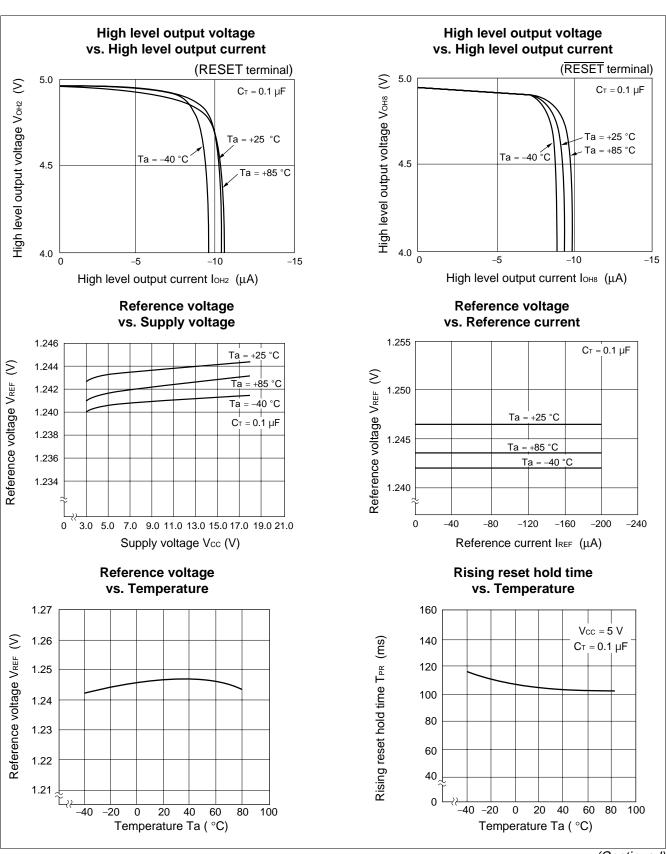

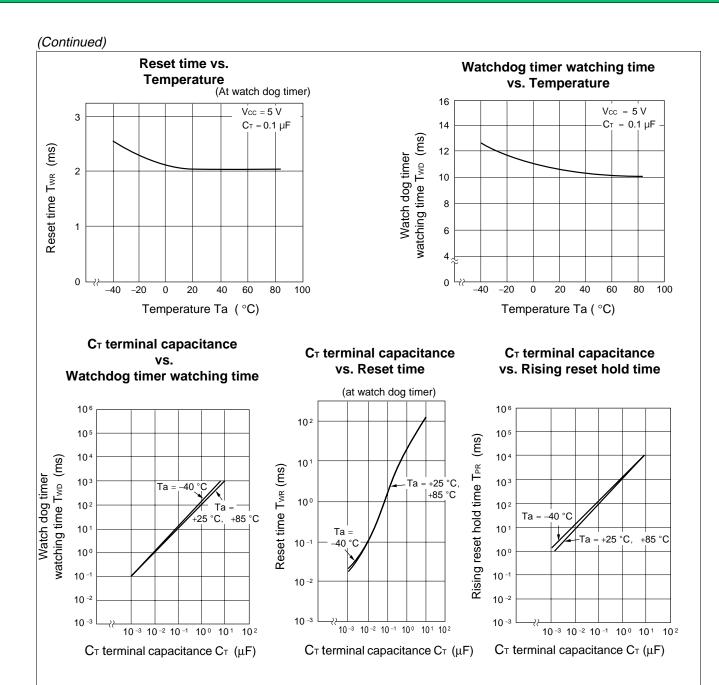

#### **■ TYPICAL CHARACTERISTIC CURVES**

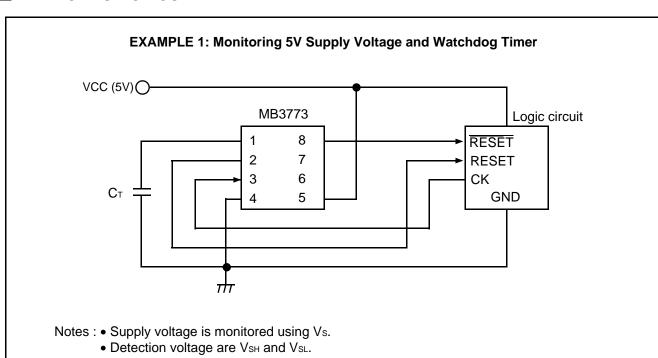

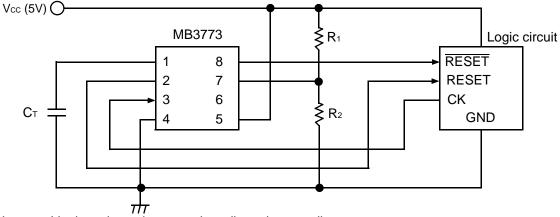

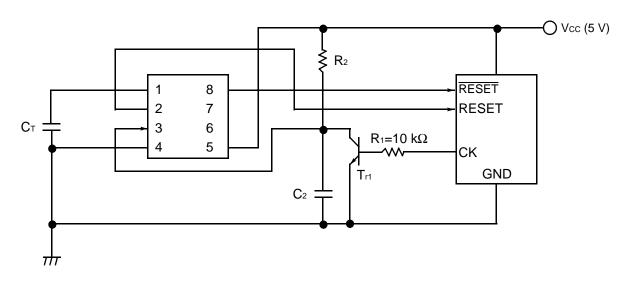

#### **■ APPLICATION CIRCUIT**

Notes: • Vs detection voltage can be adjusted externally.

• Based on selecting R<sub>1</sub> and R<sub>2</sub> values that are sufficiently lower than the resistance of the IC's internal voltage divider, the detection voltage can be set according to the resistance ratio of R<sub>1</sub> and R<sub>2</sub> (See the table below.)

| R <sub>1</sub> (kΩ) | R <sub>2</sub> (kΩ) | Detection voltage: V <sub>SL</sub> (V) | Detection voltage: Vsн (V) |

|---------------------|---------------------|----------------------------------------|----------------------------|

| 10                  | 3.9                 | 4.4                                    | 4.5                        |

| 9.1                 | 3.9                 | 4.1                                    | 4.2                        |

13

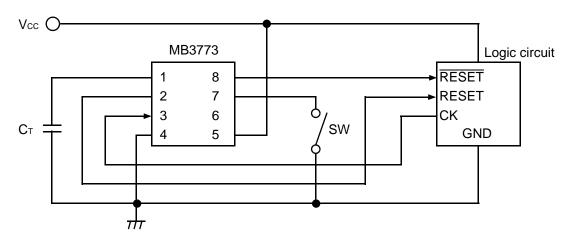

#### **EXAMPLE 3: With Forced Reset (with reset hold)**

(a)

Note: Grounding pin 7 at the time of SW ON sets RESET (pin 8) to Low and RESET (pin 2) to High.

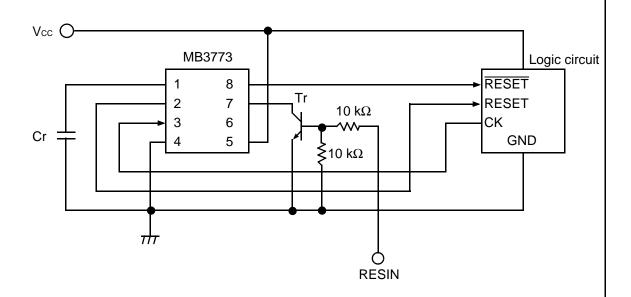

(b)

Note : Feeding the signal to terminal RESIN and turning on Tr sets the  $\overline{\text{RESET}}$  terminal to Low and the RESET terminal to High.

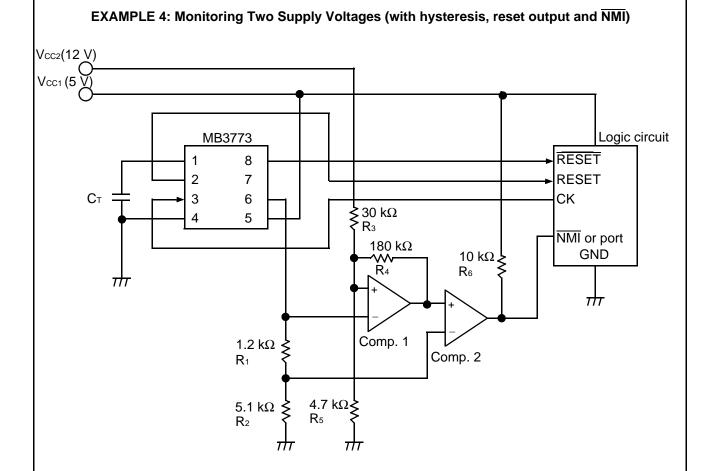

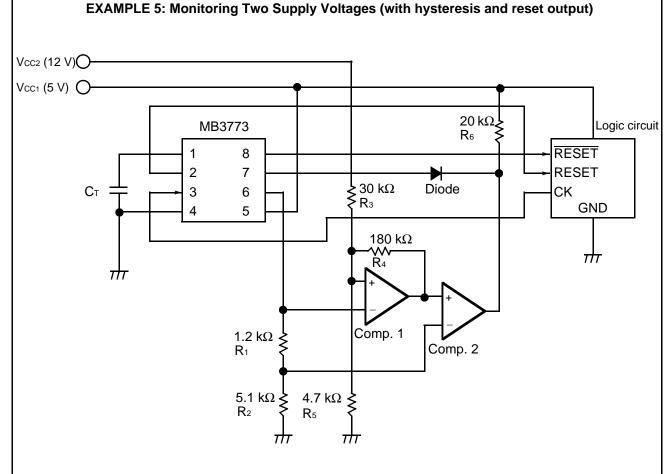

Example : Comp. 1, Comp. 2 : MB4204, MB47393

Notes: • The 5 V supply voltage is monitored by the MB3773.

- The 12 V supply voltage is monitored by the external circuit. Its output is connected to the NMI terminal and, when voltage drops, Comp. 2 interrupts the logic circuit.

- Use Vcc1 (= 5 V) to power the comparators (Comp. 1 and Comp. 2) in the external circuit shown above.

- $\bullet$  The detection voltage of the Vcc2 ( = 12 V) supply voltage is approximately 9.2 V/9.4 V and has a hysteresis width of approximately 0.2 V.

Vcc2 detection voltage and hysteresis width can be found using the following formulas:

$\rightarrow$  Hysteresis width  $V_{HYS} = V_{2H} - V_{2L}$

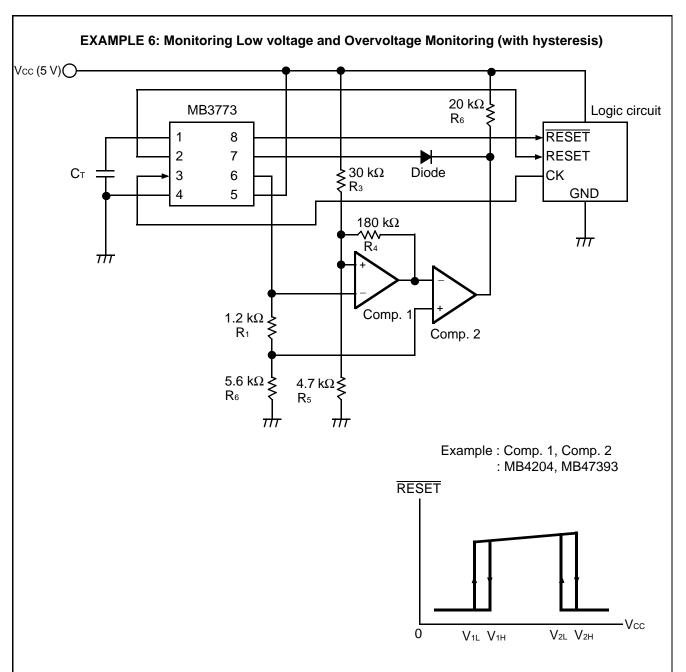

Example : Comp. 1, Comp. 2 : MB4204, MB47393

Notes: • When either 5 V or 12 V supply voltage decreases below its detection voltage (V<sub>SL</sub>), the MB3773 RESET terminal is set to High and the MB3773 RESET terminal is set to Low.

- Use Vcc1 ( = 5 V) to power the comparators (Comp. 1 and Comp. 2) in the external circuit shown above.

- The detection voltage of the Vcc2 ( = 12 V) supply voltage is approximately 9.2 V/9.4 V and has a hysteresis width of approximately 0.2 V. For the formulas for finding hysteresis width and detection voltage, see section 4.

Notes: • Comp. 1 and Comp. 2 are used to monitor for overvoltage while the MB3773 is used to monitor for low voltage. Detection voltages V<sub>1</sub>L/V<sub>1</sub>H at the time of low voltage are approximately 4.2 V/4.3 V. Detection voltages V<sub>2</sub>L/V<sub>2</sub>H at the time of overvoltage are approximately 6.0 V/6.1 V. For the formulas for finding hysteresis width and detection voltage, see EXAMPLE 4.

• Use Vcc ( = 5 V) to power the comparators (Comp. 1 and Comp. 2) in the external circuit shown above.

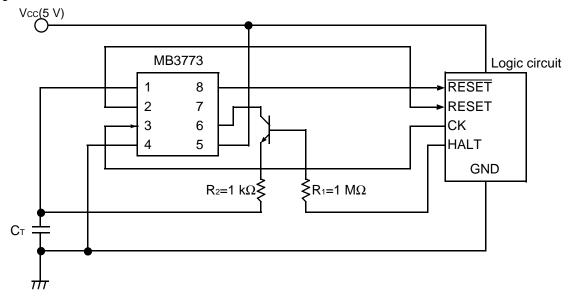

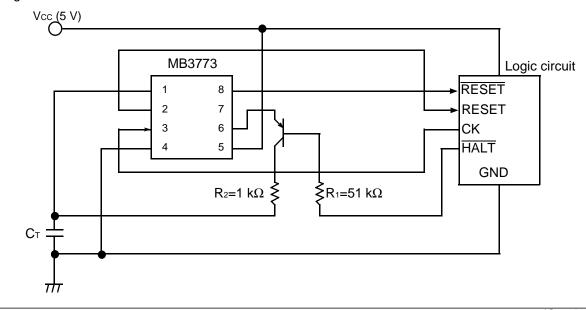

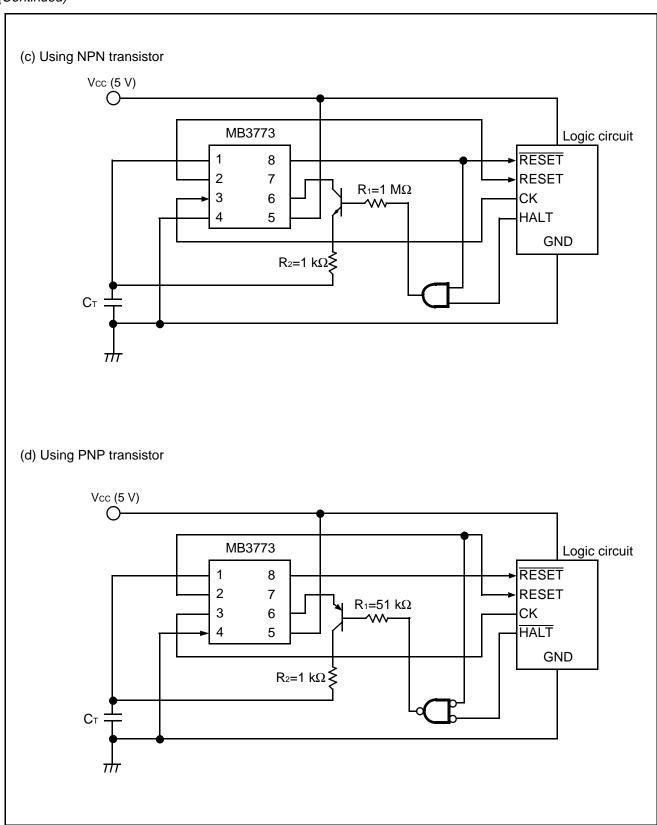

#### **EXAMPLE 8: Stopping Watch-dog Timer (Monitoring only supply voltage)**

These are example application circuits in which the MB3773 monitors supply voltage alone without resetting the microprocessor even if the latter, used in standby mode, stops sending the clock pulse to the MB3773.

• The watch-dog timer is inhibited by clamping the C<sub>T</sub> terminal voltage to V<sub>REF</sub>.

The supply voltage is constantly monitored even while the watch-dog timer is inhibited.

For this reason, a reset signal is output at the occurrence of either instantaneous disruption or a sudden drop to low voltage.

Note that in application examples (a) and (b), the hold signal is inactive when the watch-dog timer is inhibited at the time of resetting.

If the hold signal is active when tie microprocessor is reset, the solution is to add a gate, as in examples (c) and (d).

#### (a) Using NPN transistor

#### (b) Using PNP transistor

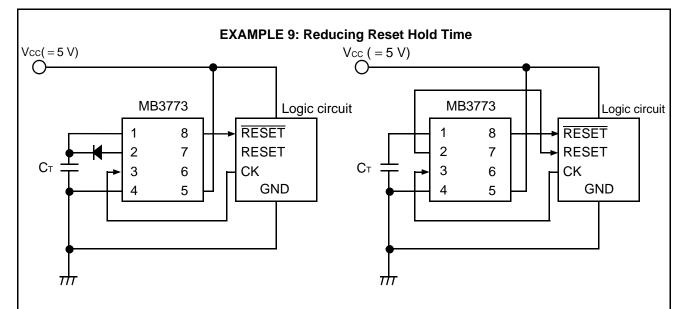

(a) TPR reduction method

(b) Standard usage

Notes: • RESET is the only output that can be used.

• Standard Tpr, Two and Twr value can be found using the following formulas.

Formulas:

$$T_{PR}$$

(ms)  $\Rightarrow$  100  $\times$  CT ( $\mu$ F)

Two (ms)

$$\Rightarrow$$

100  $\times$  CT ( $\mu$ F)

Twr (ms)

$$\Rightarrow$$

16  $\times$  CT ( $\mu$ F)

• The above formulas become standard values in determining Tpr, Two and Twr. Reset hold time is compared below between the reduction circuit and the standard circuit.

$C_T=0.1~\mu F$

|      | TPR reduction circuit | Standard circuit |

|------|-----------------------|------------------|

| Tpr≑ | 10 ms                 | 100 ms           |

| Two≑ | 10 ms                 | 10 ms            |

| Twr≑ | 1.6 ms                | 2.0 ms           |

#### **Description of Application Circuits**

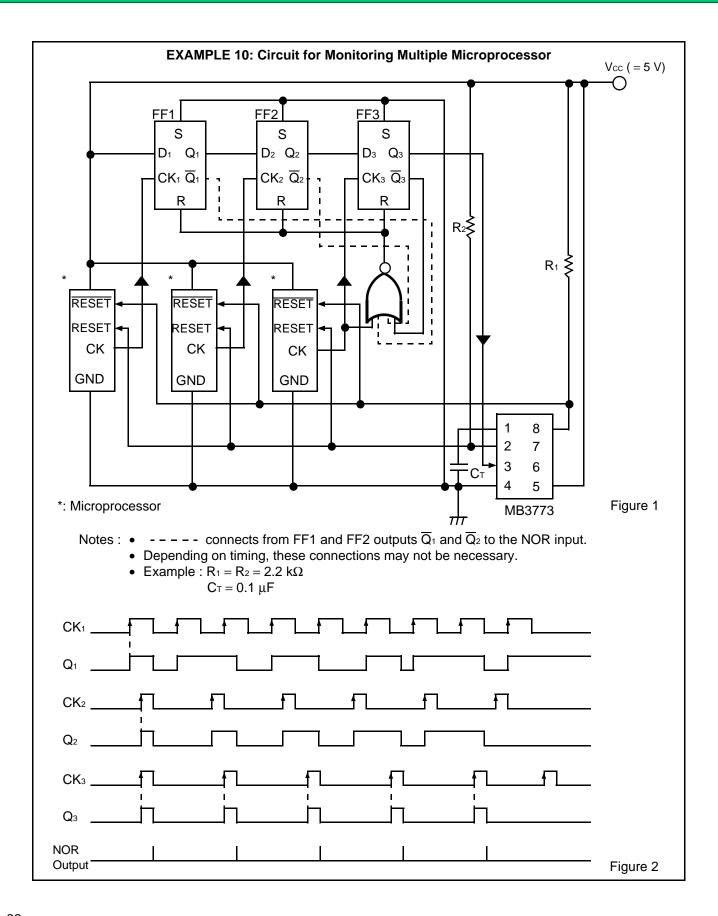

Using one MB3773, this application circuit monitors multiple microprocessor in one system. Signals from each microprocessor are sent to FF1, FF2 and FF3 clock inputs. Figure 2 shows these timings. Each flip-flop operates using signals sent from microprocessor as its clock pulse. When even one signal stops, the relevant receiving flip-flop stops operating. As a result, cyclical pulses are not generated at output Q<sub>3</sub>. Since the clock pulse stops arriving at the CK terminal of the MB3773, the MB3773 generates a reset signal.

Note that output Q<sub>3</sub> frequency f will be in the following range, where the clock frequencies of CK1, CK2 and CK3 are f<sub>1</sub>, f<sub>2</sub> and f<sub>3</sub> respectively.

$$\implies \frac{1}{f_0} \le \frac{1}{f} \le \frac{1}{f_1} + \frac{1}{f_2} + \frac{1}{f_3}$$

where  $f_0$  is the lowest frequency among  $f_1$ ,  $f_2$  and  $f_3$ .

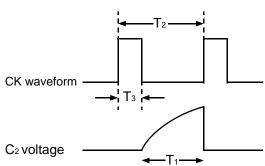

**EXAMPLE 11: Circuit for Limiting Upper Clock Input Frequency**

- Notes: This is an example application to limit upper frequency fH of clock pulses sent from the microprocessor.

- If the CK cycle sent from the microprocessor exceeds fH, the circuit generates a reset signal. (The lower frequency has already been set using  $C_T$ .)

- When a clock pulse such as shown below is sent to terminal CK, a short T<sub>2</sub> prevents C<sub>2</sub> voltage from reaching the CK input threshold level (\(\dip 1.25\) V), and will cause a reset signal to be output. The T<sub>1</sub> value can be found using the following formula:

$$T_1 \doteqdot 0.3~C_2R_2$$

where  $V_{CC} = 5~V,~T_3 \ge 3.0~\mu s,~T_2 \ge 20~\mu s$

Example: Setting C and R allow the upper T1 value to be set (See the table below).

| С       | R     | <b>T</b> 1 |

|---------|-------|------------|

| 0.01 μF | 10 kΩ | 30 μs      |

| 0.1 μF  | 10 kΩ | 300 μs     |

#### **■ NOTES ON USE**

- Take account of common impedance when designing the earth line on a printed wiring board.

- Take measures against static electricity.

- For semiconductors, use antistatic or conductive containers.

- When storing or carrying a printed circuit board after chip mounting, put it in a conductive bag or container.

- The work table, tools and measuring instruments must be grounded.

- The worker must put on a grounding device containing 250 k $\Omega$  to 1 M $\Omega$  resistors in series.

- Do not apply a negative voltage

- Applying a negative voltage of –0.3 V or less to an LSI may generate a parasitic transistor, resulting in malfunction.

#### **■** ORDERING INFORMATION

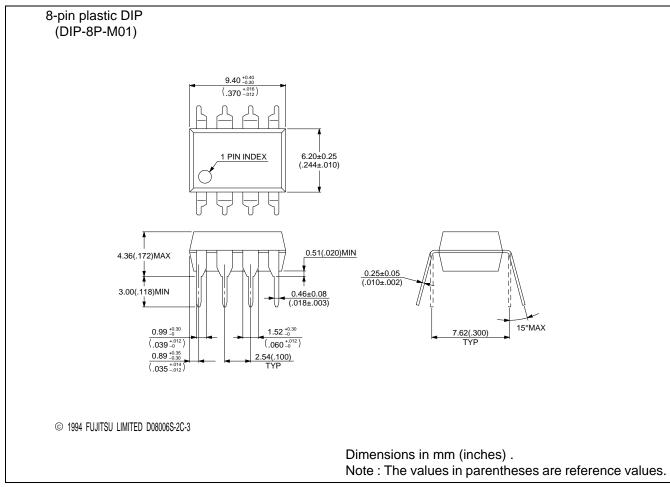

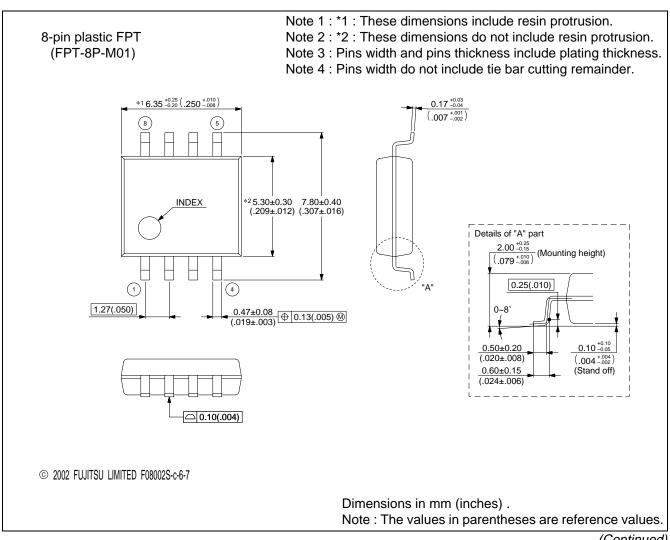

| Part number | Package                           | Remarks |

|-------------|-----------------------------------|---------|

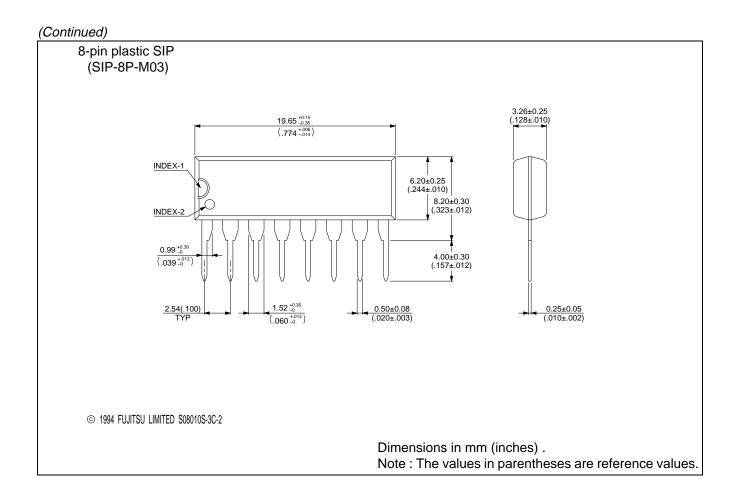

| MB3773P     | 8-pin plastic DIP<br>(DIP-8P-M01) |         |

| MB3773PS    | 8-pin plastic SIP<br>(SIP-8P-M03) |         |

| MB3773PF    | 8-pin plastic SOP<br>(FPT-8P-M01) |         |

## **■ PACKAGE DIMENSIONS**

## **FUJITSU LIMITED**

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

#### F0308

© FUJITSU LIMITED Printed in Japan